# **Ceramic Packages**

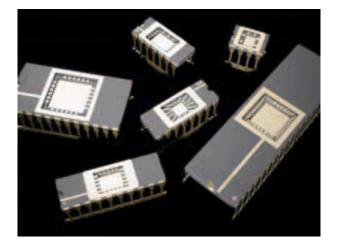

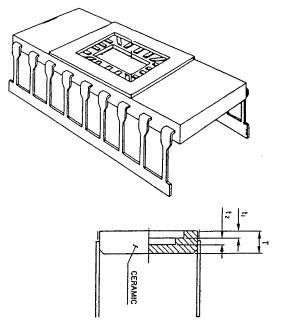

#### **Ceramic Side Braze**

Ceramic Side Braze are one of the most popular multilayer packages due to high-reliability and performance as well as ease of assembly. Also known as Dual-in-Line Packages (DIP or DIL), they have dominated the electronics industry for twenty years.

- Multilayer Ceramic Package

- Footprint Equal to Cerdip and PDIP Packages

- Through Hole Assembly Easy Soldering and Removal Techniques

- Good Heat Dissipation Airflow Above and Below Package

- Solder, Glass or Epoxy Seal

- Lead Plating: Gold or Solder Dip

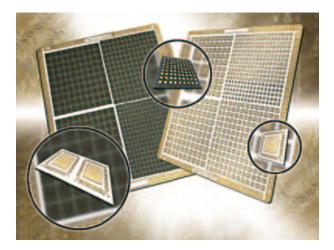

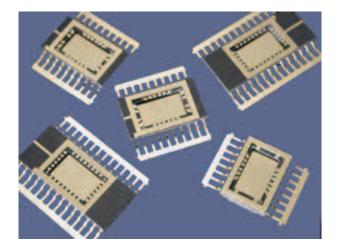

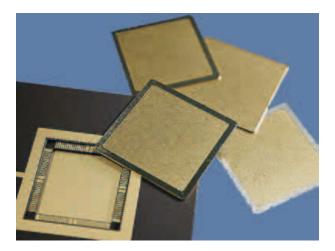

### **Chip Scale Packages**

We now offer standard leadless Chip Scale Packages. These CSPs use Plated and Bonded Copper (PBC) on alumina ceramic for superior electrical and thermal conductivity. PBC technology offers a thermal advantage of 8x-10x over laminates or LTCC. The electrical conductivity advantage is more than 5x over conventional thick film. RF loss testing shows PBCs are among the best of all ceramic interconnection technologies, at frequencies from DC to 50 GHz. The panels are standard "as-fired" 5.0" x 7.0" size with a common thickness of 0.025". All machining is performed by laser to obtain the fine dimensions required for high-density circuits. The electroplated and fired plated-copper conductor used is more than 99.9% pure. It can be electroplated in thick (12um-125um) patterns on the ceramic substrate.

- Cost-effective solution for low, medium or high volumes

- Short lead time--one to two weeks

- Low tooling (pattern) cost

- Compatible with wire bond or flip chip applications

- Rugged, low-loss, leadless design

- Fine lines and spaces (.003" or 75 micron min.)

- High thermal conductivity substrates

- Low dielectric loss

- Low moisture absorption

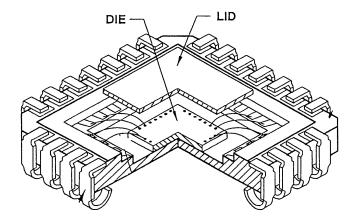

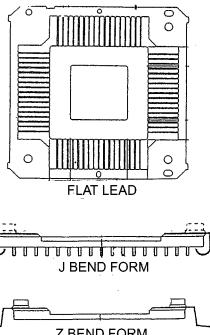

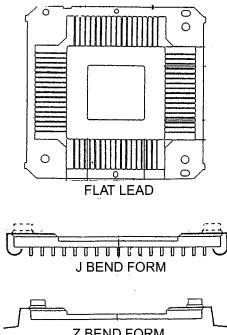

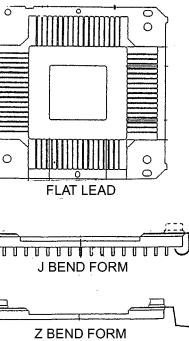

#### Ceramic Quad Flat Pack J-Bend

The multilayer construction and solder seal characteristics of the Ceramic Quad Flat Pack provide excellant electrical performance and thermal management. The external lead frame is formed into a J-shape to allow for socketing or direct board soldering. The leads allow this package to expand and contract during heating and cooling cycles without placing undue stress on the package to PCB connection.

- Multilayer Ceramic Package

- Footprint Compatible with LCC and PLCC

- Surface Mount or Socket Applications

- Gold Plated Leads

- Solder, Glass or Epoxy Seal

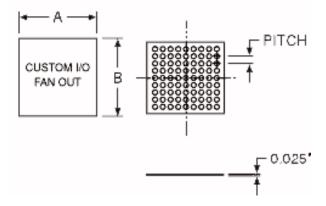

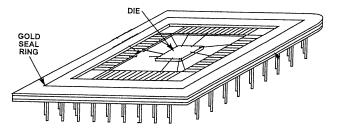

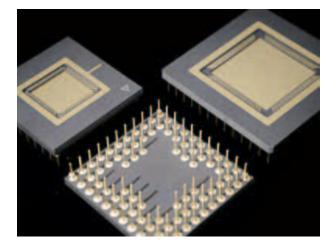

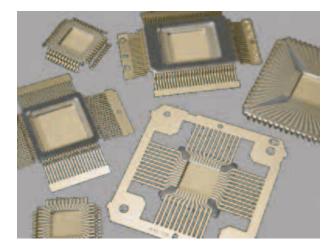

## Ceramic Pin Grid Arrays

Ceramic Pin Grid Array Packages offer high I/O signal carring capacity, excellent electrical performance and high thermal heat dissipation, with minimum package size. This through-hole mount package is typically square in shape with gold-plated pins brazed in a matrix pattern to the bottom of the package. CPGAs are designed for low inductance and enhanced thermal performance. Higher lead counts offer cavity down orientation for potential application of a Heat Sink to assist in thermal dissipation.

- Multilayer Ceramic Package

- Footprint Compatible with PPGA

- Through Hole or Socket Mount

- Variety of Body Sizes

- Gold Plated Leads

- Solder, Glass or Epoxy Seal

- Cavity Up or Cavity Down Configurations

4

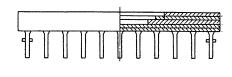

## **Ceramic SOIC**

The SOIC is an ideal package for telecommunication, automotive, and other applications that require dense placement of chips an boards. It is a surface mount package with .050" lead spacing. Ceramic SOICs are currently only manufactured in 16, 20, 24, and 28 lead configurations.

- Multilayer Ceramic Package

- Surface Mount

- Comparable Foot Print With Wide Body SOP

Plastic Packaging

- Solder, Glass or Epoxy Seal

- Gull Wing Lead Configuration

- Gold Plated Leads

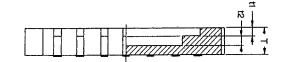

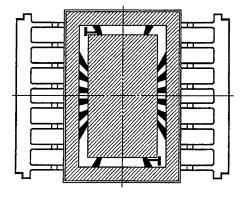

### Metal Alloy Lids

Our Combination Lid/Preform Assemblies offer the highest standard of seal reliability and true hermetic performance. The Lid is Kovar or Alloy 42 base material with multilayer gold and nickel plating per MIL-M-38510. The Lid thickness is .010" or .015". The Perform is 80/20 Gold/Tin alloy with a standard thickness of .0021". The Lid OD should be .025" less than the package seal ring OD and the Lid ID should be .045" larger than the package seal ring ID, provided a minimum solder width of .025" is maintained.

- Perfect Alignment of Lid and Preform

- Only One Part to Handle

- Corrosion Resistance

- Moisture Resistance

- Marking Permanency

6

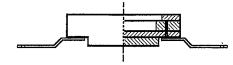

## **Ceramic Lids Glas / Epoxy**

Ceramic Lids are used on various multilayer packages where temperature constraints after die attach require low temperature lid seal. Ceramic Lids come in a wide variety of shapes, sizes and thicknesses. They can be fabricated from a single pressed layer of ceramic or a multilayer construction where a cup shaped lid is required. Ceramic Lids may also incorporate glass or quartz windows for EPROM applications.

- Flat or Cup Shaped

- Low Temperature Epoxy or Glass Seal

- Solid or Window Options

- Marking Permanency

# **Ceramic Cerquad**

The Cerquad or Quad Cerpac Base and Cap is a pressed powder, single layer package consisting of either a square or rectangular shaped base, top coated with a non-vitreous glass. A lead frame is embedded into the glass to create both internal die connection and external board connection. An additional layer known as a Window Frame can be fabricated on top of the lead frame creating an elevated flat surface to accommodate a flat ceramic lid. Non-Window Frame versions must use a cup shaped lid.

- Pressed Ceramic Package

- Footprint Compatible with PQFP

- Surface Mount

- Lead Form: Flat, Gull Wing, J-Bend

- Lead Plating: Gold, Solder Dip or Tin

- Bond Finger Plating: Gold or Aluminium

- EIAJ or JEDEC Configurations

- Glass or Epoxy Seal

#### CAP / EPROM

#### FRIT LID

8

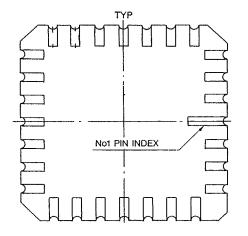

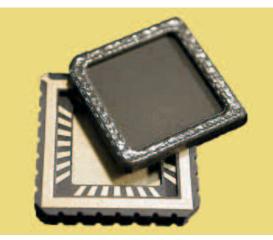

### **Ceramic Leadless Chip Carriers**

JEDEC type Leadless Chip Carriers continue their popularity for surface mount applications. The Leadless Chip Carrier's low profile, multilayer construction offers short internal electrical traces from the die to the metalized castellations around all sides and bottom of the package. These outside contacts are normally .040" or .050" on center. JEDEC outlines come in Type A, B, C, D, or E configurations.

- Low Profile, Multilayer Ceramic PackageFootprint Compatible with CQJB and PLCC

- Variety of Body Sizes

- Solder, Glass, or Epoxy Seal

- Castellations Instead of Leads

- Socket or Surface Mount Package

- Lead Plating: Gold or Solder Dip